当前,计算机系统结构的发展正面临新的机遇。过去,应用负载在不同阶段分别表现为计算型和事务型的特征,系统结构针对不同的特征,分别以“算得快”和“数据移动快”为目标发展了高性能计算机系统。随着云计算与大数据的发展,信息化进入了第三个阶段,负载特征随之变成了通量型,对计算机系统的设计提出了新的挑战。笔者预测“强化控制”将成为系统结构研究的新目标。在过去几年里,中科院计算所在强化控制的研究上进行了一些探索,取得了一些效果。

计算机的三个基本部件

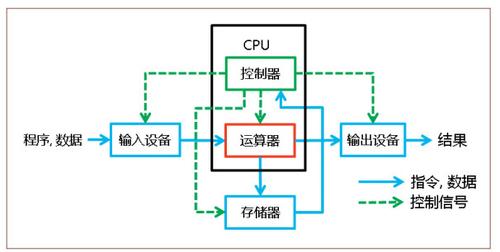

从1946年第一台通用计算机ENIAC,到2016年超级计算机Top500榜首的神威·太湖之光[1],计算机的发展一直采用冯·诺伊曼体系结构。在冯·诺伊曼体系结构中,计算机由五个部件组成:运算器、控制器、存储器、输入设备和输出设备。数据和由指令组成的程序通过输入设备输入到计算机,存储在存储器中;控制器中的程序计数器(program counter)指示计算机从存储器中取出程序指令,存放到指令寄存器(instruction register)中;控制器根据取到的指令对运算器进行控制,指示运算器进行算术或逻辑运算,必要时会把运算结果写回存储器,或者通过输出设备输出结果。如图1所示。程序输入并存储到计算机中后,整个计算机就在程序的控制下进行工作。到目前为止,冯·诺伊曼体系结构仍然是现代计算机的基础。

图1 冯·诺伊曼体系结构

回顾70年的计算机发展史,可以粗略地把信息化划分为三个阶段:IT 1.0单机计算阶段,IT 2.0人机通信阶段和IT 3.0人机物三元融合阶段。这三个阶段的应用负载分别具有不同的特征,这些负载特征驱动着计算机系统结构的主要进步。本文将冯·诺伊曼体系结构中的五个部件归纳成三个基本部件:(1)包含运算器的计算部件,(2)包含存储器、输入设备和输出设备的数据通路部件,(3)包含控制器的控制部件。这样归纳是因为笔者观察到,在每个阶段,冯·诺伊曼体系结构中相应的基本部件都成为该阶段的改进重点,颠覆性技术也主要从该基本部件中产生。

提高计算机性能的基本方法

IT 1.0单机计算阶段

这个阶段大致在1946~1980年间,从第一台通用计算机ENIAC开始,到互联网开始流行前,计算都是计算机的首要任务。

ENIAC(Electronic Numerical Integrator And Computer)即“电子数值积分计算机”,冯·诺伊曼使用它进行氢弹相关的计算[2],后来又被用于计算中子在不同物质中穿越的距离,减轻了开发核弹的科学家原来雇用大量人力进行的计算[3]。国内计算机的用途一开始也是军事领域的计算任务,例如1967年中科院计算所高庆狮等人领导制造的“109丙”机用于核弹和火箭研究,被称为两弹一星功勋计算机[4]。

在IT 1.0阶段,计算机的应用负载主要为计算型负载(computation workload)。这类负载主要基于物理模型和数学公式,计算量是可预测的。完成单个任务所需要的时间一般在几小时到几天,对实时性要求不高。在计算型负载的驱动下,计算机追求的是“算得快”,强化冯·诺伊曼体系结构中的计算部件就成为了计算机发展的首要目标。

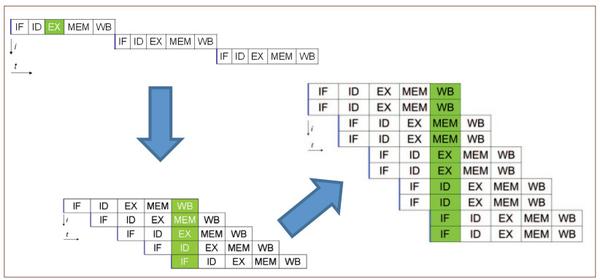

让计算机“算得快”主要有两种方法。第一种方法是提高并行度。一开始计算机指令是一条一条地串行执行的,指令流水线技术把一条指令分成若干阶段,不同指令的不同阶段可以并行执行(见图2)。该技术首先在伊利诺伊大学1962年制造的计算机ILLIAC II中采用[5]。进一步提出的超标量技术,在计算部件中添加更多的功能部件,使得位于相同阶段的多条指令也能并行执行,首先用在了CDC公司1964年制造的CDC 6600计算机中[6]。CDC 6600还有一项重要的贡献被载入史册:第一次实现了乱序执行[6]。乱序执行技术是一种带窗口的数据流执行模型,让与正在执行的指令无数据依赖的后续指令先执行,提高了指令级并行度。

图2 提高指令级并行度的方法

除了提高指令级并行度,单指令多数据 (Single Instruction Multiple Data, SIMD)技术着眼于从数据级并行提高并行度,通过一条指令同时处理多个数据;多处理器技术(SMP)则利用线程级并行,通过多个处理器同时进行工作来提高并行度。这两项技术最早都是在20世纪60年代出现的,在对数据访问读写顺序进行控制的基础上提高了计算机的并行度和性能。

第二种方法是利用局部性。局部性原理是指程序在访问一段数据后,在不久的将来再次访问相同的数据(时间局部性),或者很快就会访问相邻的数据(空间局部性)。计算机科学家在60年代观察到这些特性,利用时空局部性对冯·诺伊曼体系结构的数据通路部件进行改进,代表性的技术包括TLB、Cache、DRAM的行缓存等。这些技术通过将经常访问的数据存放在一个高速的存储中,访问数据时先到高速的存储中查看,如果数据存在则直接访问,数据不存在时才会访问相对慢速的存储设备。

在IT 1.0阶段,控制技术的进步主要体现在对共享的使能上。共享的使能使得一台大型机可以像多台小机器那样同时使用,用户在一台大型机上同时运行多个不同的任务而不会相互干扰。最为重要的两项共享技术也是在60年代产生的,一项技术是分时共享,通过划分时间片的方式让不同的任务轮流使用CPU,第一个分时共享系统是麻省理工学院(MIT)在1961年制造的兼容分时系统(Compatible Time-Sharing System, CTSS)[7];另一项技术是虚拟内存,向程序提供统一的虚拟地址空间,在微结构中添加内存管理单元(MMU)来进行虚拟地址到物理地址的转换,保证不同程序的物理地址空间不会产生干扰,从而在不同任务之间实现内存的共享。

纵观整个IT 1.0阶段,颠覆性创新大多与计算部件相关。

IT 2.0人机通信阶段

IT 2.0阶段大致在1980~2010年,个人电脑(PC)逐渐流行,越来越多的普通人开始使用计算机,互联网的出现使得人与人、人与机、机与机之间的交互变得越来越频繁。20世纪90年代初,在时任副总统戈尔的推动下,美国开始实施“信息高速公路”国家战略计划,大兴网络基础设施建设,互联网用户呈现爆发式增长,在线视频会议、网络电话、网络购物等新兴应用大量涌现出来。

与IT 1.0阶段有所不同,普通用户很少产生纯粹意义上的计算需求,更多地,只是发起鼠标点击、信息查找、浏览网页等请求,计算机更多地是在进行数据的搬运。这种负载称为事务型负载(transaction workload)。对计算机来说,事务型负载是由外界产生的,具有不可预测性。由于人机交互特性的存在,处理单个负载的耗时一般在秒级,具有一定的实时性,否则用户就难以忍受了。在事务型负载的驱动下,计算机追求的是“数据移动快”,强化冯·诺伊曼体系结构的数据通路部件就转变为计算机发展的首要目标。

让计算机“数据移动快”有两种主要方法。第一种方法是扩大存储器规模。全对称共享存储技术(SMP)在80年代是非常热门的研究点,该技术让处理单元共享一个容量较大的存储器,通过读写共享数据的方式进行通信,是一种快速的数据移动方式。分布式共享存储技术(DSM)通过把物理上分布在不同机器上的存储器抽象成一个统一的逻辑存储器,从而形成更大规模的存储器,并在逻辑存储器的层次进行数据的传递。普林斯顿大学教授李凯在1986年提出的共享虚拟存储技术(SVM)[8]是分布式共享存储的一种软件实现,物理上分布在不同机器中的存储器,在操作系统的页面层次进行共享。这些扩大存储器规模的技术都需要对缓存一致性进行相应的控制,以保证数据传递的正确性。

第二种方法是提高互联能力,扩大系统的规模。ccNUMA是一种可扩展的分布式共享存储架构,通过在硬件上维护缓存一致性实现大规模处理单元的互联。早期使用该架构的例子有SGI公司1996年发布的Origin2000,国防科技大学1997年制造的银河-III巨型计算机也使用了ccNUMA架构,计算速度达到了每秒130亿次[9]。另一种最主流的互联技术是Cluster架构(机群),用通用互联网络对通用计算机进行大规模的互联,早期的例子有IBM公司1994年发布的SP2,加州大学伯克利分校1997年发布的NOW项目(Network of Workstations)。中科院计算所1998年制造的曙光2000也使用了机群架构,计算速度达到了每秒200亿次[9]。大规模并行处理(Massive Parallel Processing , MPP)架构是一种最可扩展的互联技术,它的一个节点由处理单元、局部存储器及网络接口电路定制而成,节点之间通过定制的高速网络进行互联,组成大规模并行计算系统。使用MPP架构的例子有Cray公司1995年发布的T3D/E,2016年6月位于超级计算机Top500榜首的神威·太湖之光也使用了MPP架构[1]。

IT 2.0阶段计算部件也有创新,例如,同步多线程技术(Simultaneous Multi-Threading, SMT)与芯片级多处理(Chip-level Multi-Processing, CMP)技术,让计算机“算得快”也是通过这些技术提高并行度实现的。但总体来说,在计算部件的创新上不如IT 1.0阶段。

在IT 2.0中,为保障事务型负载秒级处理的实时性,通常使用软件技术来强化控制就可达到目的。例如,通过CPU调度算法为实时性要求较高的应用分配更多的时间片,通过页面调度算法将热页面尽可能保留在内存中,通过“优先读,延迟写”技术降低读操作的延迟,提高应用的响应时间,通过通信掩藏技术在数据通信的同时进行计算,将通信开销隐藏在计算中,等等。

纵观整个IT 2.0阶段,颠覆性创新大多与数据通路部件相关。

IT 3.0人机物三元融合阶段

IT 3.0阶段大致从2010年开始,物联网、云计算、大数据、人工智能等名词也开始流行。通过物联网,大量的设备和智能物体被“连接”进赛博空间(Cyberspace),“云上”的中心计算机可以实现对机器、设备、人员的集中管理,以及控制和服务。通过收集小数据,聚集与分析大数据,一些智能应用逐渐产生。如减少车祸、都市规划、灾害预测与犯罪防治,流行病控制等。据IBM统计,2012年每天大约产生2.5EB1的数据[10]。要充分发挥这些数据的价值,就需要在云端对EB级大数据进行高速智能处理。

应用负载的特征再次发生改变,IT 3.0阶段的负载属于通量型负载(throughput workload)。通量型负载有两个显著的特点,一是负载量非常大。谷歌在2015年的一次报告中披露,数据中心的一台16核心的服务器平均需要在600微秒内处理40个远程过程调用(RPC)请求[11]。照此计算,一台服务器在1秒内就需要处理约67000个RPC请求,处理单个通量型负载的耗时要求缩短到毫秒、甚至亚毫秒级别。另一个显著特点是负载的种类多样。哥伦比亚大学研究人员在2011年发现,在短短的7分钟内,谷歌数据中心1000台服务器就运行了1102个不同的应用[12],这些应用的特征各不相同,有批处理类型,有延迟敏感类型。在通量型负载的驱动下,计算机追求的目标不是单一的“算得快”或“数据移动快”,而是“算得多”。

处理通量型负载的巨大挑战之一是对共享资源不确定性的强竞争。通量型负载的“负载量大”说明对共享资源的竞争非常强烈,“种类多样”说明竞争具有不确定性。从2010年开始,学术界已经有一批工作对计算机系统中暴露的每一处共享干扰点进行研究(见表1)。事实上,强竞争不仅仅发生在软件层次,体系结构层次的运算资源、数据通路、网络资源也引入了大量的不确定性,具体表现为访存粒度小(计算/访存比低),访存特征随机(访存模式不规则),数据通路冲突严重(访存并发度大)。在资源竞争冲突严重时,系统的实际性能会出现“断崖式”急剧下降。

表1 学术界发现的竞争共享点

谷歌在2006年就开始注意到这个问题了。他们发现谷歌数据中心的大部分请求都能在60毫秒内被处理,但受到不确定强竞争的影响时,部分请求需要花费1800毫秒才能完成处理,造成长尾延迟现象[11]。谷歌的工程师们尝试了软件层次的各种细粒度控制技术,有名的包括任务调度框架Borg、容器化技术docker、容器部署框架kubernetes、用户态协议栈DPDK等。这些软件调度技术可以降低可预测的竞争,例如谷歌内部的批处理作业,但无法降低不可预测的竞争,例如用户发起的请求。美国工程院院士迪克·赛茨(Dick Sites)在2015年的报告中将通量型负载对数据中心服务器提出的新挑战,列为谷歌遇到的三大难题之一[11]。

当前,通过众核提高并发度来强化计算部件,通过硅光器件提高通信带宽来强化数据通路部件,都无法从根本上解决上述问题。通量型负载需要强控制,强化控制部件是IT 3.0阶段计算机发展的首要目标。

中科院计算所的工作

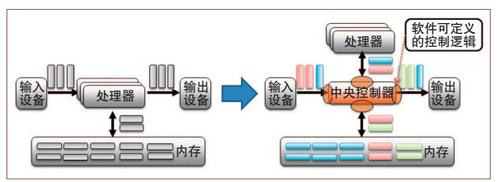

包云岗等在《中国计算机学会通讯》(CCCF)2016年第3期上发表文章,从高熵系统和网络服务质量(QoS)的角度介绍了中科院计算所的几个工作。本文从计算机控制部件的角度重新审视这些工作,体现体系结构技术进步的本质。为了强化控制部件,中科院计算所提出了“标签化冯·诺伊曼体系结构”(Labeled von Neumann Architecture, LvNA)思路,如图3所示。它是在冯·诺伊曼结构上的一个扩展:借助标签化技术,通过在体系结构层提供软件定义功能,实现硬件资源的有序控制。在这个思路的指导下,计算所提出了三项强化控制的技术。

图3 标签化冯·诺伊曼体系结构

资源可编程体系结构(PARD)

资源可编程体系结构(Programmable Architecture for Resourcing-on-Demand, PARD)如图4所示。PARD是一种针对数据中心的服务器技术,目标是在不确定强竞争环境下保障高优先级应用的服务质量。

图4 PARD体系结构

PARD具备三点关键技术:

● 在处理器核心添加可编程的控制标签寄存器,硬件请求带着控制标签进行传播,请求从传统的“地址”强化为“地址+标签”,实现地址空间的标签化(labeled address space)。

● 在共享资源处添加基于标签的可编程控制逻辑,根据请求的控制标签进行区分化的控制,访问共享资源的功能从传统的“预取”强化为“预取+分配”。

● 添加全局管理模块,连接所有控制标签寄存器和控制逻辑,对其进行编程式管理。

PARD也因此具备了新特性:(1)全硬件虚拟化:在不需要VMware/Xen/KVM等虚拟层管理程序(hypervisor)的情况下,可将一台物理服务器划分为多个子机器,直接加载操作系统,运行应用;(2)硬件支持的实时监控:开销小于1毫秒级的无开销实时监控,使智能调度成为可能;(3)硬件支持的服务质量:实现了硬件隔离,消除干扰,保障服务响应时间,可以把数据中心CPU的平均利用率从20%提升到60%。

PARD已完成了基于现场可编程门阵列(FPGA)的概念验证系统,阶段性成果由包云岗等在计算机体系结构顶级会议ASPLOS 2015上发表,与华为公司联合申请了包括多个高价值专利的专利群,正在开展PARD原型系统的研制。

消息式内存架构

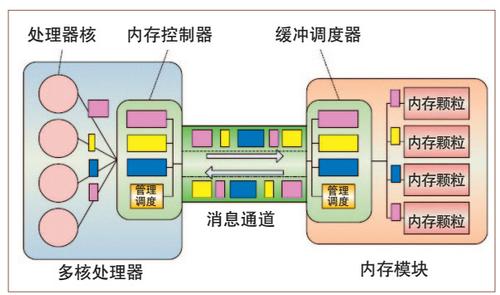

中科院计算所提出的另一个强化控制技术是“消息式内存架构”。这是一种基于异步请求/应答消息的新型访存协议。详见图5。

图5 消息式内存架构

消息式内存改变了延用几十年的同步式内存系统,用“消息包访存”取代基于缓存块的“总线访存”。这种方式带来诸多好处:首先,消除了总线对时序的约束,可将访存并发度提升一个数量级,支持超过1024个并发请求;其次,消息式内存支持8B~4KB的可变粒度访存请求;第三,消息式内存的控制器便于增加控制逻辑,增强了对内存通路的控制能力。

消息式内存工作完成了基于FPGA的原型系统,采用基准测试程序HPCC中有关内存性能的部分,在ARM Cortex A9处理器平台上与标准DDR3进行了比较。在顺序访存的Stream测试中,通过消息自动完成大粒度数据搬移,消息式内存性能比DDR提高 70%;在随机细粒度访存Random Access测试中,通过将多个细粒度内存读写命令转换成异步分散-收集(Scatter-Gather)请求,提高了并发度和传输效率,消息式内存访存带宽达到DDR内存总线的4倍。

消息式内存研究已申请发明专利40多项,其中18项是国际专利合作条约(Patent Cooperation Treaty , PCT)专利,包括已进入实审阶段的6项美国、欧盟专利,核心专利转让给华为公司后获得华为“创新总裁奖”,当前正与华为公司合作开展产品化工作。

片上请求收集表

针对处理通量型负载的众核处理器,为了支持片上数据通路的全局可控,中科院计算所提出了访存请求收集表机制(M-Table),以及相应的高密度片上网络、线程级硬件调度表(T-Table)。M-Table负责对片上访存请求进行全局调度,实验表明,采用该机制后,访存数量减少约49%,访存带宽提高约24%,平均执行速度提高约89%。对于高通量应用,高密度片上网络的平均吞吐率比传统片上网络提高了22.2%,SPLASH-2基准测试的性能提高了13.5%。借助于T-Table,可以在不同截止期限的要求下将实时任务的成功率提高1~3倍。

图6 DPU-m芯片及加速卡系统

基于上述技术,计算所针对数据中心的高通量视频处理开发了DPU-m原型芯片,见图6。该芯片基于TSMC 40nm工艺,功耗不超过4W,与英特尔相同工艺下的主流芯片Sandy Bridge相比,面积效率提升70倍,性能功耗比提升80~240倍,相关成果发表在Hot Chips、IEEE Micro等顶级期刊与会议上。目前,基于DPU-m原型芯片构建的高通量视频计算系统已经在国家重要的网络视频监管与分析领域试用。

结语

表2 不同阶段的负载特征与颠覆性技术

表2对IT三个阶段的负载特征和颠覆性技术进行了总结。IT 1.0阶段的负载主要是计算型负载,颠覆性技术多从强化计算部件中产生;IT 2.0阶段主要是事务型负载,颠覆性技术多从强化数据通路部件中产生;IT 3.0阶段主要是通量型负载,笔者预测这一阶段的颠覆性技术可能更多地从强化控制部件中产生。

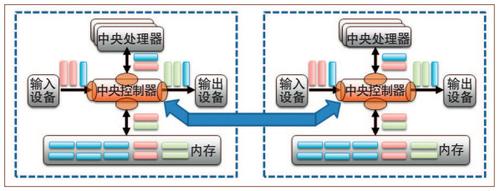

图7 未来架构猜想

在未来的计算机结构中,冯·诺伊曼体系结构可能会增加一个独立于中央处理器(CPU)的部件“中央控制器”,对整个计算机进行集中式的控制,可扩展系统则通过中央控制器进行互联,并实现数据中心整机级别的控制,进而实现跨越端网云的端到端的延迟可控。见图7。■

1 1EB=1018B。

参考文献

[1] China Tops Supercomputer Rankings with New 93-Petaflop Machine[OL]. (2016-01-20).https://www.top500.org/news/china-tops-supercomputer-rankings-with-new-93-petaflop-machine/.

[2] Goldstine, Herman H.The Computer: from Pascal to von Neumann[M]. Princeton University Press, ISBN 0-691-02367-0, 1972.

[3] Kean S.The Disappearing Spoon[M].New York: Little, Brown and Company, ISBN 978-0-316-05163-7, 2010: 109-111.

[4] 高庆狮.http://baike.baidu.com/view/65238.htm.

[5] Brearley H C. ILLIAC II - A Short Description and Annotated Bibliography[J]. IEEE Transactions on Electronic Computers, 1965: 399-401.

[6] Hill M D, Jouppi N P, Sohi G S. Readings in Computer Architecture[M].Morgan Kaufmann, ISBN 978-1558605398, 1999: 11.

[7] Mccarthy J. Reminiscences on the History of Time-Sharing[J]. IEEE Annals of the History of Computing, 1983, 14(1):19-24.

[8] Li K, Hudak P, Memory coherence in shared virtual memory systems[J]. ACM Transactions on Computer Systems, 1989, 7(4): 321-359.

[9] 维基百科.中国超级计算机[OL].https://zh.wikipedia.org/wiki/%E4%B8%AD%E5%9B%BD%E8%B6%85%E7%BA%A7%E8%AE%A1%E7%AE%97%E6%9C%BA.

[10] IBM. What is big data? – Bringing big data to the enterprise[OL].(2013-08-26). http://www.ibm.com/big-data/us/en/.

[11] Sites D.Datacenter Computers modern challenges in CPU design, Google, Feb. 2015.

[12] Kambadur M, Moseley T, Hank R, et al. Measuring interference between live datacenter applications[C]// SC '12: Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis.IEEE, 2012:1-12.